ADI解析未來工廠 基于AI傳感器的邊緣決策——人工智能應用軟件開發篇

在《ADI解析未來工廠》系列的第一部分中,我們探討了搭載人工智能的傳感器在邊緣設備中的作用及其硬件基礎。本文作為該系列的第二部分,將聚焦于人工智能應用軟件開發——這是實現邊緣智能決策的核心環節。

一、邊緣AI應用軟件的核心作用

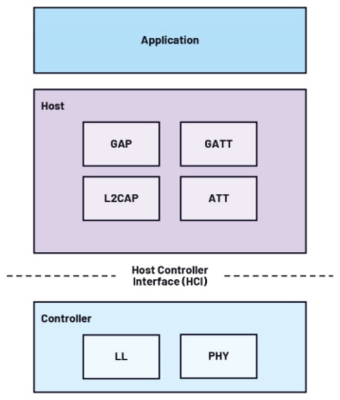

在工業4.0和工業物聯網背景下,邊緣AI應用軟件承擔著連接傳感器數據與智能決策的橋梁作用。這類軟件通常包含數據預處理、模型推理、決策邏輯和通信接口四大模塊。通過優化算法和輕量化設計,軟件能夠在資源受限的邊緣設備上高效運行。

二、開發流程與方法

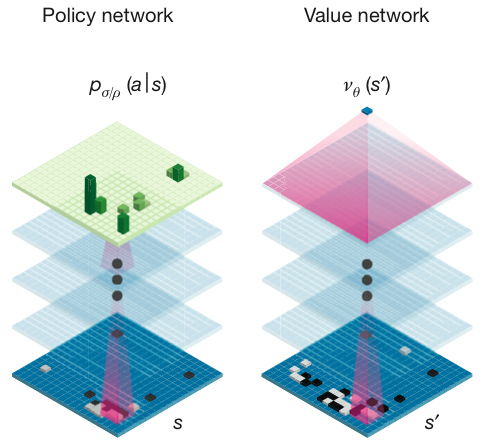

- 模型選擇與優化:基于工廠場景需求(如異常檢測、預測性維護),選擇適當的機器學習模型(如CNN、LSTM或Transformer)。考慮到邊緣設備的計算和存儲限制,常采用模型剪枝、量化和知識蒸餾等技術進行優化。

- 數據流水線設計:構建從傳感器到決策的數據流。這包括實時數據采集、噪聲過濾、特征提取和數據增強。軟件需支持多傳感器融合,以提升決策的準確性和魯棒性。

- 邊緣推理引擎集成:利用TensorFlow Lite、ONNX Runtime或專用SDK(如ADI的跨平臺方案),將訓練好的模型部署到邊緣設備。重點優化推理延遲和能效,確保實時響應。

- 決策邏輯與自適應學習:開發基于規則的決策模塊,并與AI模型輸出結合。例如,當傳感器檢測到設備振動異常時,軟件可自主觸發停機或調整參數。部分高級應用還支持在線學習,通過聯邦學習持續改進模型。

三、實際應用案例

在預測性維護場景中,AI應用軟件通過分析振動傳感器數據,提前識別電機故障跡象。軟件在邊緣端完成推理,直接向控制系統發送維護警報,減少云端依賴和延遲。類似地,在質量檢測中,視覺傳感器結合目標檢測模型,實時分揀瑕疵產品,顯著提升生產線效率。

四、開發挑戰與趨勢

當前邊緣AI軟件開發仍面臨模型兼容性、安全性和跨平臺部署等挑戰。未來趨勢包括:

- 低代碼/無代碼平臺:簡化開發流程,讓領域專家參與應用構建。

- 邊緣-云協同:通過分層架構平衡邊緣實時性與云端大數據分析。

- 標準化與開源生態:促進工具鏈互通,加速產業化落地。

結語

人工智能應用軟件開發是釋放邊緣傳感器潛力的關鍵。隨著軟件工具的成熟和生態系統的完善,未來工廠將邁向更智能、自適應和高效的新階段。在下一部分中,我們將深入探討邊緣AI系統與云平臺的集成策略。

如若轉載,請注明出處:http://www.drwallms.cn/product/27.html

更新時間:2026-04-08 00:42:39