集成電路設計實踐 從運放設計入門到精通

集成電路設計是現代電子工業的核心,而運放設計則是模擬集成電路中最基礎、最重要的模塊之一。本文將以《集成電路設計實踐 運放設計 901602518.pdf》為引,探討運放設計的核心概念與實踐方法,幫助初學者快速入門。

一、運放設計的基礎知識

運放(運算放大器)是一種高增益、差分輸入的電壓放大器,廣泛應用于信號調理、濾波、模數轉換等電路中。設計一個高性能的運放,需要掌握以下基礎知識:

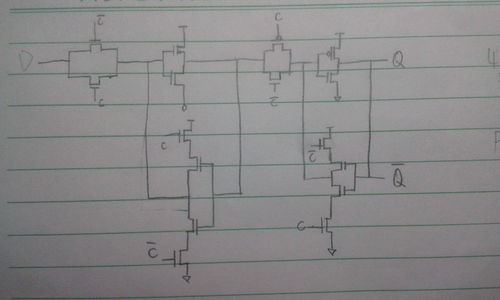

- 基本結構:包括差分輸入級、增益級、輸出級和偏置電路。

- 關鍵參數:如開環增益、帶寬、相位裕度、共模抑制比(CMRR)、電源抑制比(PSRR)等。

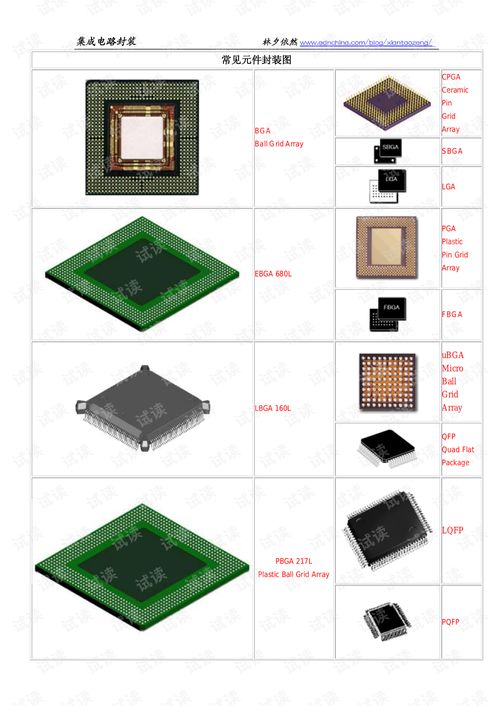

- 工藝選擇:根據設計需求選擇合適的CMOS或BiCMOS工藝。

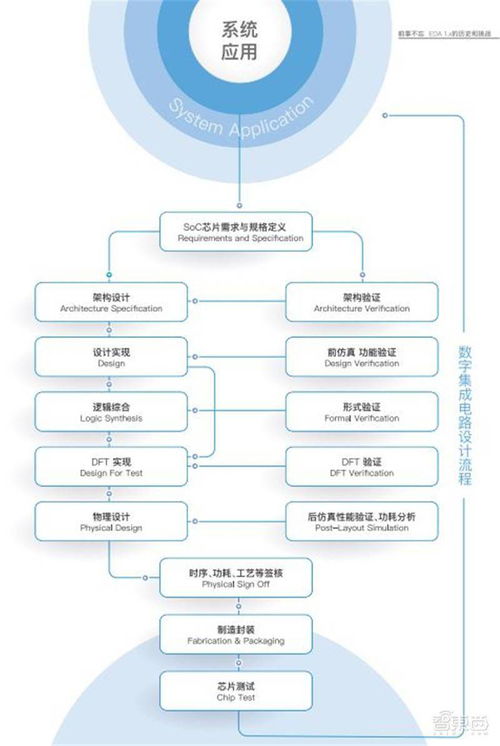

二、運放設計的實踐步驟

- 需求分析:明確運放的性能指標,如增益、帶寬、功耗、噪聲等。

- 電路拓撲選擇:根據需求選擇適合的拓撲結構,如折疊共源共柵、兩級運放等。

- 器件尺寸設計:通過手工計算或仿真工具確定晶體管的尺寸,確保電路滿足性能要求。

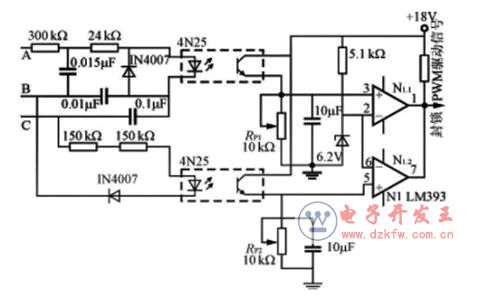

- 仿真驗證:使用仿真工具(如Cadence、HSPICE)進行直流、交流、瞬態和噪聲仿真,優化電路性能。

- 版圖設計:繪制電路的物理版圖,考慮匹配、寄生效應和可靠性問題。

- 后仿真:提取版圖寄生參數后再次仿真,確保電路性能不受版圖影響。

三、常見問題與解決方法

- 穩定性問題:通過米勒補償或前饋補償提高相位裕度,避免振蕩。

- 噪聲優化:增大輸入對管尺寸或采用低噪聲結構降低噪聲。

- 功耗與性能權衡:根據應用場景調整偏置電流,平衡功耗與速度、增益的關系。

四、進階設計技巧

對于高性能運放設計,還需關注以下方面:

- 低電壓設計:在深亞微米工藝下,采用共模反饋(CMFB)或新型結構適應低電源電壓。

- 高精度設計:通過校準技術或斬波調制降低失調電壓和噪聲。

- 系統集成:將運放嵌入更復雜的系統中,如ADC、PLL,考慮整體性能優化。

五、學習資源推薦

除了《集成電路設計實踐 運放設計 901602518.pdf》外,建議參考以下資源:

- 經典教材:《模擬集成電路設計》(拉扎維著)、《CMOS模擬集成電路設計》(艾倫著)。

- 實踐工具:Cadence、Synopsys等EDA工具,結合開源工具如ngspice進行仿真。

- 在線社區:EETOP等專業論壇,參與討論并獲取實際項目經驗。

運放設計是集成電路設計的基石,需要理論與實踐緊密結合。通過系統學習基礎知識、勤于仿真實踐,并不斷優化設計方法,工程師可以逐步掌握高性能運放的設計能力,為更復雜的集成電路開發打下堅實基礎。

如若轉載,請注明出處:http://www.drwallms.cn/product/65.html

更新時間:2026-02-12 15:35:22